## 2008

## M.Sc.

# 3rd Semester Examination

### **ELECTRONICS**

#### PAPER-EL-2101

Full Marks: 50

Time: 2 hours

The figures in the right-hand margin indicate full marks.

Candidates are required to give their answers in their own words as far as practicable.

Illustrate the answers wherever necessary.

Answer Q. No. 1 and any three questions from the rest.

- 1. a) How many memory location can be addressed by a microprocessor with 14 address lines?

- b) Explain: why are the program counter and the stack pointer 16-bit registers?

(Turn Over)

- c) Explain the need to demultiplex the bus  $AD_7 AD_0$ .

- d) Determine the control word for the following configuration of the ports of Intel 8255:

Port A → Input. Mode of Port A → Mode 1

Port B → Output. Mode of Port B → Mode 0

Port  $C_{lower}$  (PC<sub>0</sub> - PC<sub>2</sub>)  $\rightarrow$  Input

- e) What are the control signals necessary in the memory mapped I/O?

2×5

- 2. a) What is the function of the accumulator of a  $8085 \mu p$ ?

- b) Write a single byte instruction that will make the content of an accumulator zero.

- c) Write an assembly language program that will multiply two eight-bit numbers using repeated addition method.

2+2+6

- **3.** a) Write an assembly language program that will convert a BCD number to a binary number.

- b) Briefly describe Opcode-fetch cycle and show the associated wave forms. 5+(3+2)

- 4. a) Indicate different data transfer schemes of 8085  $\mu$ p.

- b) Show the differences between synchronous and asynchronous data transfer schemes.

- c) Discuss different Interrupts present in 8085  $\mu$ p.

- d) What do you mean by device polling?

- e) What is vectored interrupt? 1+2+3+2+2

- 5. a) What is DMA?

- b) Indicate the function of HOLD and HLDA pins of  $8085 \mu p$ .

- c) Explain how the 8237 DMA controller transfers 64K bytes of data per channel with eight address lines.

- d) Explain How 8237 DMA controller can be used both in Master mode and Slave mode. 1+2+3+4

- 6. a) Specify the handshake signals and their functions if port A of the 8255A is set up as an output port in Mode 1.

- b) Write down the two control words that are necessary to set the bit PC<sub>6</sub>. (Assume that other ports are not being used.)

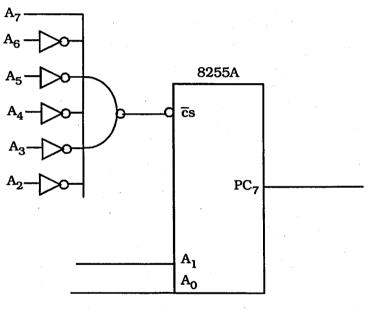

c) Find out the address of Port A, B, C and CWR using the following figure and also write a BSR control word subroutine to set PC<sub>7</sub> and reset it after 10 msec. (Assume that delay subroutine is available.)

2+2+(2+4)

Ref. Fig. No. 6.c)

Internal Assessment — 10